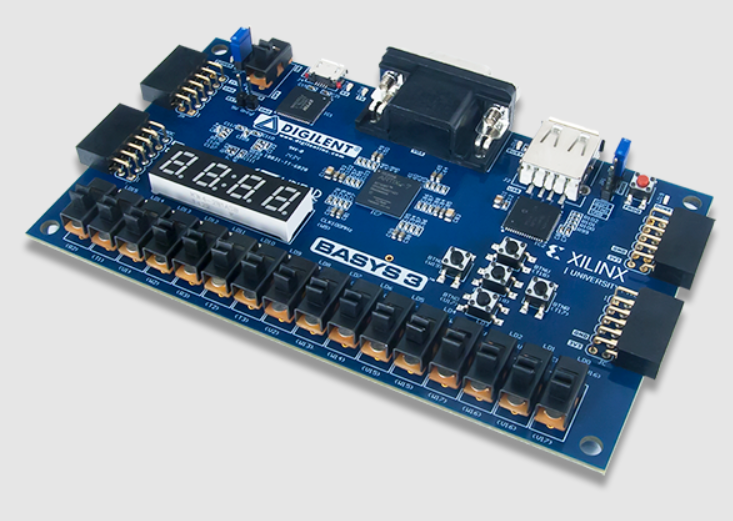

2024.6.17 수업날오늘은 저번주에 배운 Verilog 연산자의 응용버전에 대해 알아보고 직접 Basys3 보드와 연결하여 결과를 살펴본다.아래의 사진은 병렬 가산기를 나타난 회로도이다.병렬 가산기란 전가산기 여러 개를 병렬로 연결한 회로이다.이 회로도를 보면 입력값이A(4개), B(4개), Cin이고, 출력값이 S(4개), Carry임을 알 수 있다. 1. full_adder_4bits_structural(구조적 모델링)병렬 가산기를 코드로 작성한 full_adder_4bits_structural의 회로도를 자세하게 살펴보면,아래와 같이 여러 개의 게이트들이 합쳐져 있는 것을 확인할 수 있다. 이제 시뮬레이션 full_adder_4bits_structural의 시뮬레이션 결과를 확인해보자.이번에는..