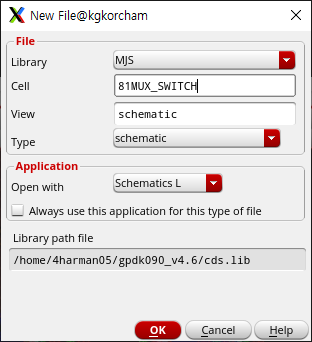

2024.11.27 수업날COMMON_SOURCE_AMP의 역할- 높은 입력 임피던스: MOSFET gate가 거의 전류를 끌어들이지 않기 때문에 입력 임피던스가 높다.- 비교적 낮은 출력 임피던스- 높은 전압 이득을 제공하여 입력 신호의 작은 변화에도 출력 신호가 크게 변한다.- 출력 신호가 입력 신호와 180도 위상이 반전된다.- 트랜지스터가 선형 영역에서 동작하도록 적절한 바이어스가 필요하다. COMMON_SOURCE_AMP schematic COMMON_SOURCE_AMP symbol COMMON_SOURCE_AMP simulation입력대비 출력이 반전 증폭된 결과를 볼 수 있다. 다음으로 증폭기의 주파수 특성을 보기 위한 AC simulation의 결과를 살펴본다. COMMO..