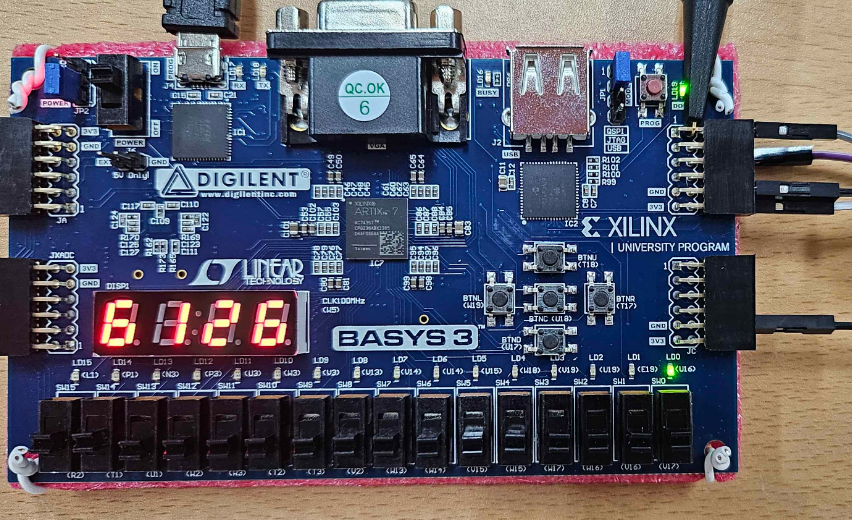

2024.7.3 수업날 오늘은 어제 습도센서를 Basys3 보드와 연결했을 때, 결과가 왜 나오지 않는지를 확인하고 이를 방지하는 방법에 대해 알아본다.Basys3 보드에 결과가 출력되지 않으면, 두가지 문제점을 고려해야한다. 하나는 코드의 문제이고, 다른 하나는 보드의 문제가 있다는 것이다. 먼저 코드에 문제가 있는지 테스트벤치(testbench)를 추가로 작성해보자. 테스트벤치란 Verilog 코드의 동작을 검증하는 시뮬레이션을 위해 필요한 파일을 만드는 것이다. 즉, 작성한 코드가 의도하는 대로 동작하는지 보는 과정이다. 테스트벤치 파일을 만드는 방법은 아래와 같다. 먼저 Add Sources에서 simulation source를 추가한다. 다음으로 Create File를 클릭하여 아래와 같이 파일..