2024.11.05 수업날

< 4NAND >

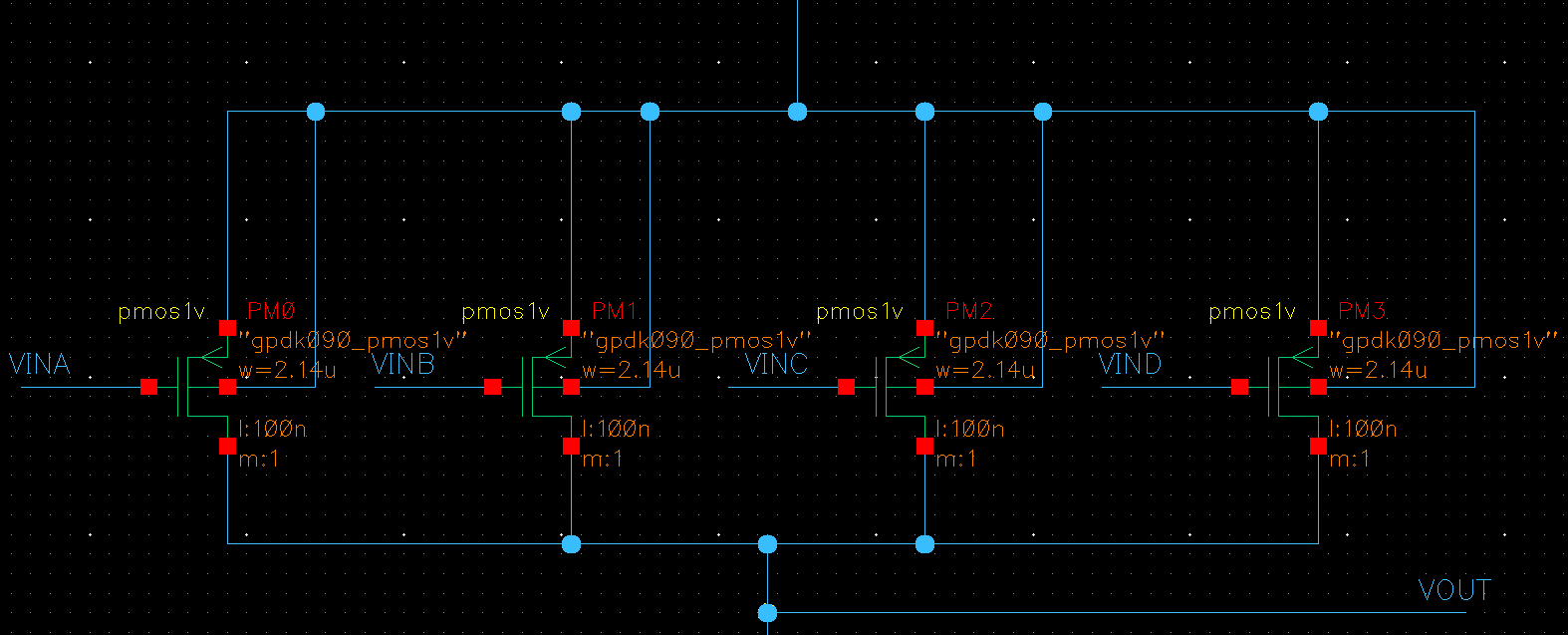

4NAND schematic

4NAND symbol

4NAND simulation

pmos W = 2.14u

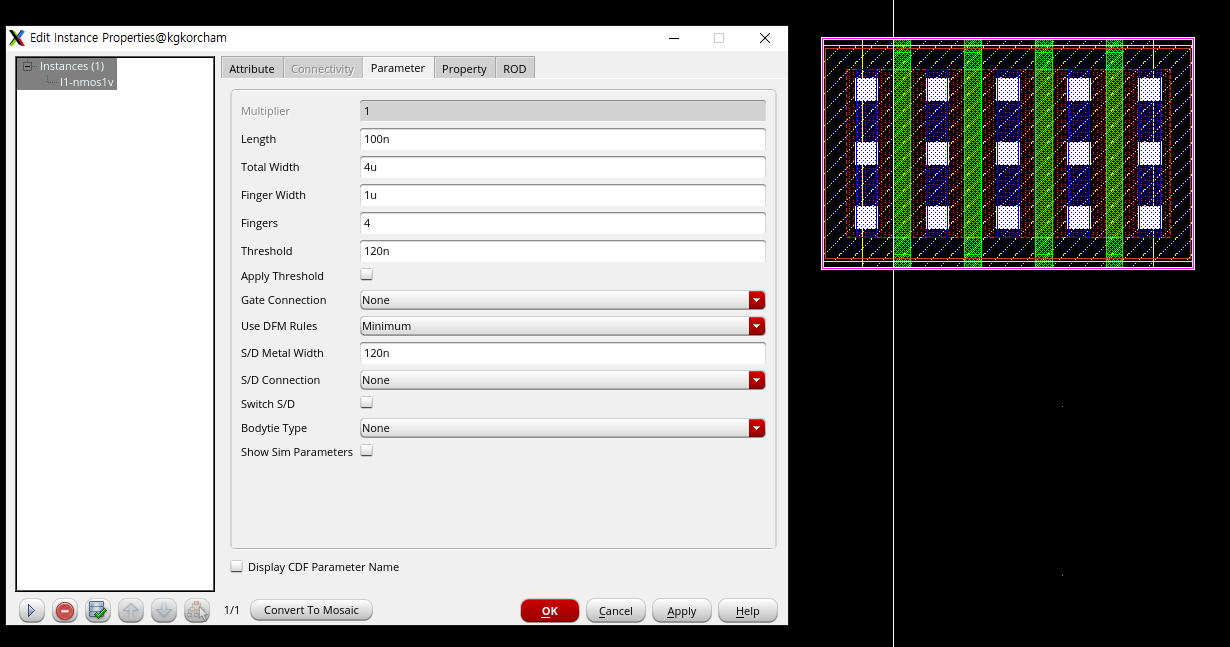

4NAND layout

4NAND schematic에서 했던대로 nmos 설정하기

4NAND schematic에서 했던대로 pmos 설정하기

layout 높이: 5.69u

layout 세부 길이

schematic 그림 보고 layout 그리기

< 4NOR >

4NOR schematic

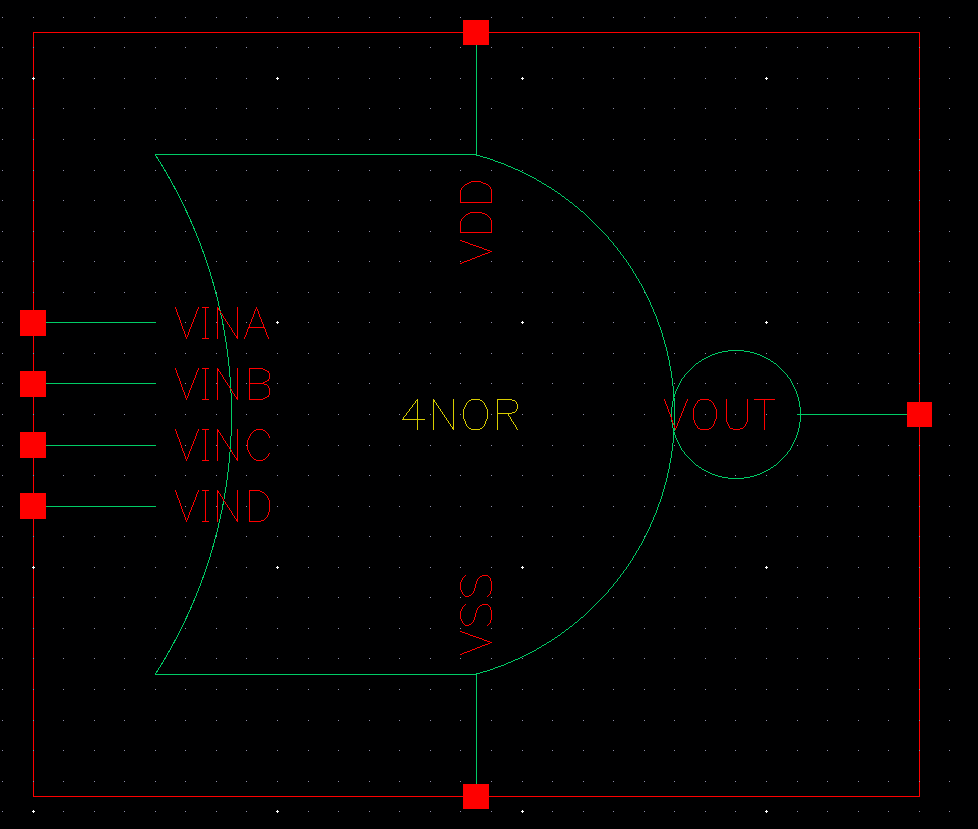

4NOR symbol

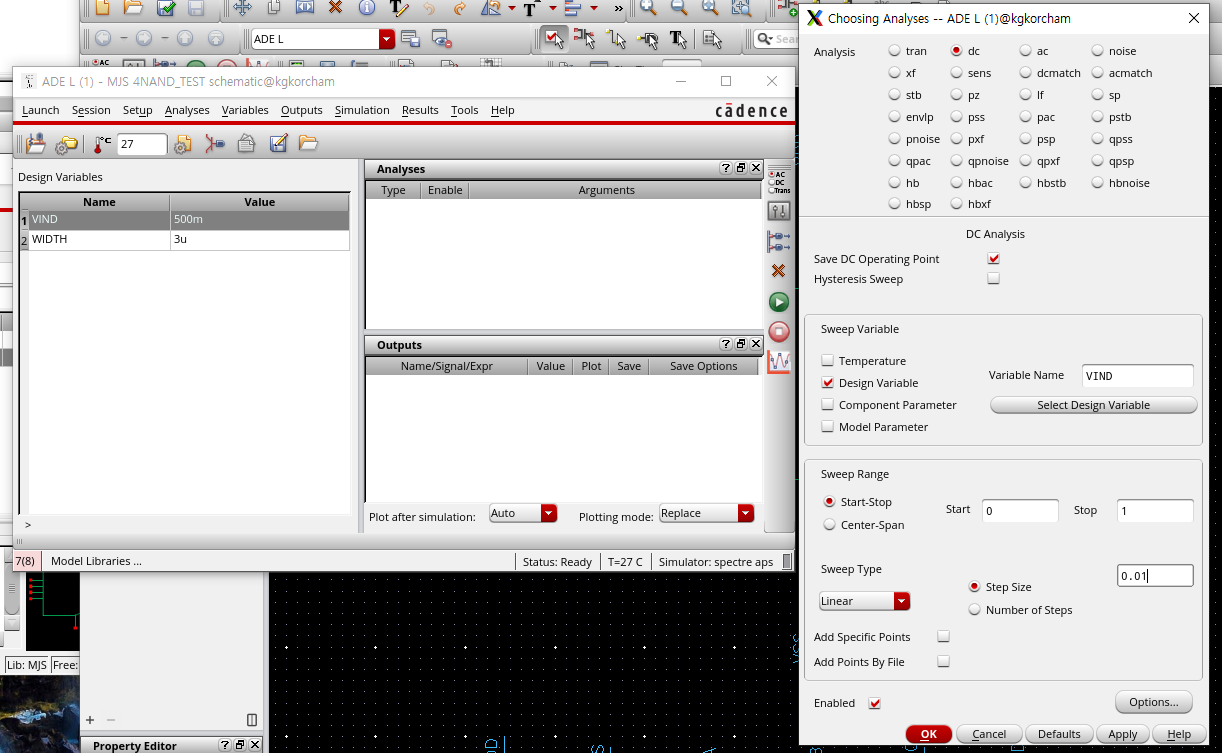

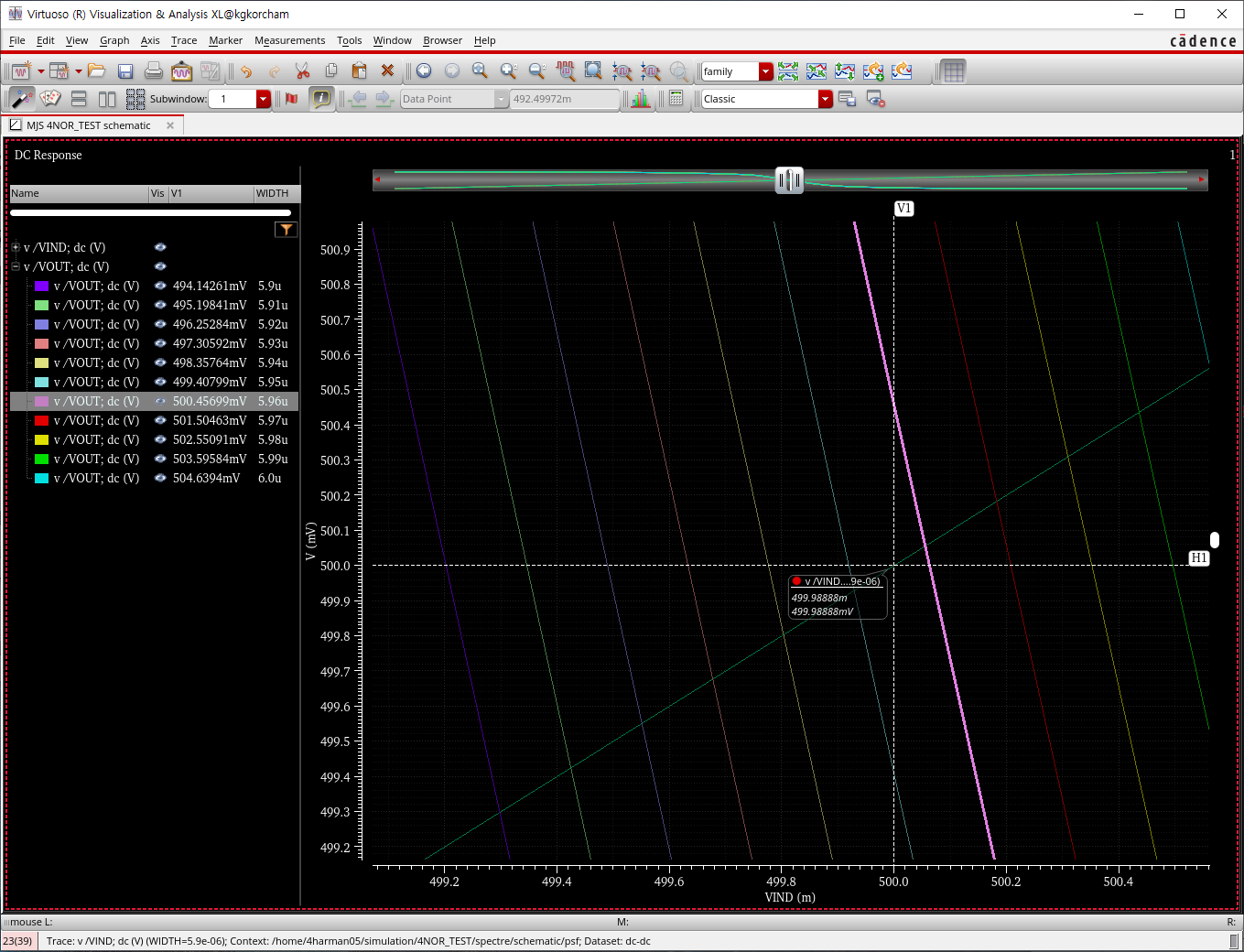

4NOR simulation

눈대중으로 500m에서 어느 그래프가 가까운지 확인하기 어렵다면

V, H 단축키를 누른 후 X, Y position을 500m으로 맞춰서 값을 확인해본다.

pmos W = 5.96u

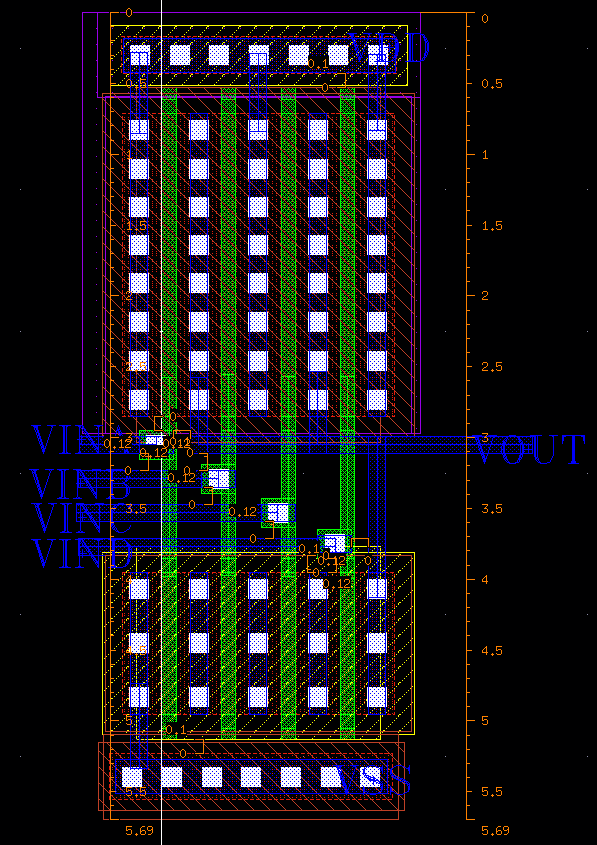

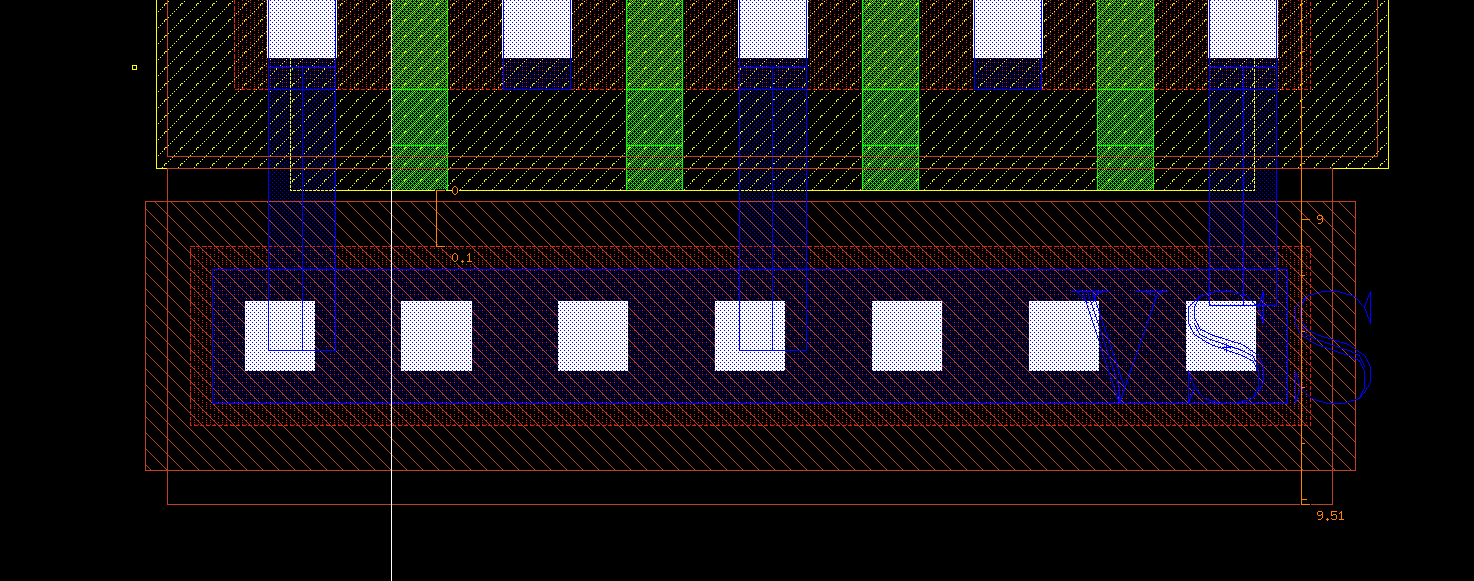

4NOR layout

4NOR schematic에서 했던대로 nmos 설정하기

4NOR schematic에서 했던대로 pmos 설정하기

layout 높이: 9.51u

layout 세부 길이

schematic 그림 보고 layout 그리기

< 21MUX_LOGIC >

21MUX_LOGIC schematic

21MUX_LOGIC symbol

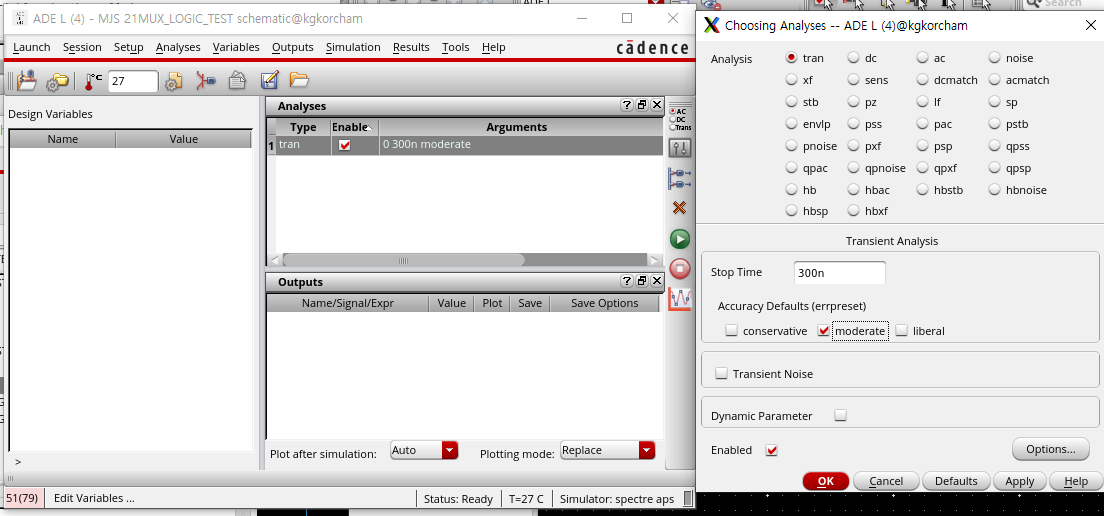

21MUX_LOGIC simulation

Variables -> Copy From Cellview를 눌렀을 때, Design Variables에서 아무것도 나타나지 않아야 정상이다.

그리고 Analyses -> choose를 선택하여 아래와 같이 설정한다.

ADE L에서 우측의 초록색 버튼을 누른 후, 시뮬레이션의 진행이 끝났다면

Results -> Direct plot -> Main Form을 선택하여 결과를 확인한다.

그리고 시뮬레이션 결과 창의 상단에 아래의 체크한 곳을 클릭하면 겹쳐져 보이던 그래프가 분리된다.

다음으로, 각 그래프의 Y축 값을 통일하기 위해

Edit -> Multi-Graph Properties를 선택하여 아래와 같이 설정한다.

최종적으로 확인할 수 있는 시뮬레이션 결과이다.

단축키 V를 눌러서 아래의 위치에 값을 표시할 수 있다.

21MUX_LOGIC layout

수업시간에 만든 자신의 라이브러리에 있는 layout을 가져와서 분리할 때는 아래와 같이 실행하면 된다.

하지만 nmos, pmos는 해제하면 안되고 합쳐진 상태로 두어야 한다.

반드시 수업시간에 만든 layout만 해제해야한다.

높이 조정은 시간 부족으로 인해 끝마치지 못했고, 각 layout의 위치가 잘 맞는지 확인해본다.

높이 조정 단계는 다음날에 해보기로 한다.

4NAND, 4NOR, 21MUX_LOGIC 진행단계 끝!