2024.8.26 수업날

< D 플립플롭 >

1. NAND gate를 사용했을 때

회로도와 SCHEMATIC

D 플립플롭 시뮬레이션 설정과 결과

2. IC 패키지를 사용했을 때

회로도와 SCHEMATIC

아래의 두 기호를 사용한다.

DigClock는 아래와 같으며 설정 값은 다음과 같다.

다음으로 IC 패키지 부분에 SOURCE를 추가한다.

D 플립플롭(IC 패키지) 시뮬레이션 설정과 결과

< JK 및 T 플립플롭 >

1. JK 플립플롭

회로도와 SCHEMATIC

JK 플립플롭 시뮬레이션 설정과 결과

2. T 플립플롭

1) CK가 ↓이고, T가 0과 1일때의 결과

회로도와 SCHEMATIC

T 플립플롭 시뮬레이션 설정과 결과

2) CK가 ↓이고, T가 0과 1이고, PR과 CLR가 각각 0과 1일때의 결과

회로도와 SCHEMATIC

T 플립플롭 시뮬레이션 설정과 결과

< 시프트 레지스터 >

1. SISO 시프트 레지스터

회로도와 SCHEMATIC

SISO 시프트 레지스터 시뮬레이션 설정과 결과

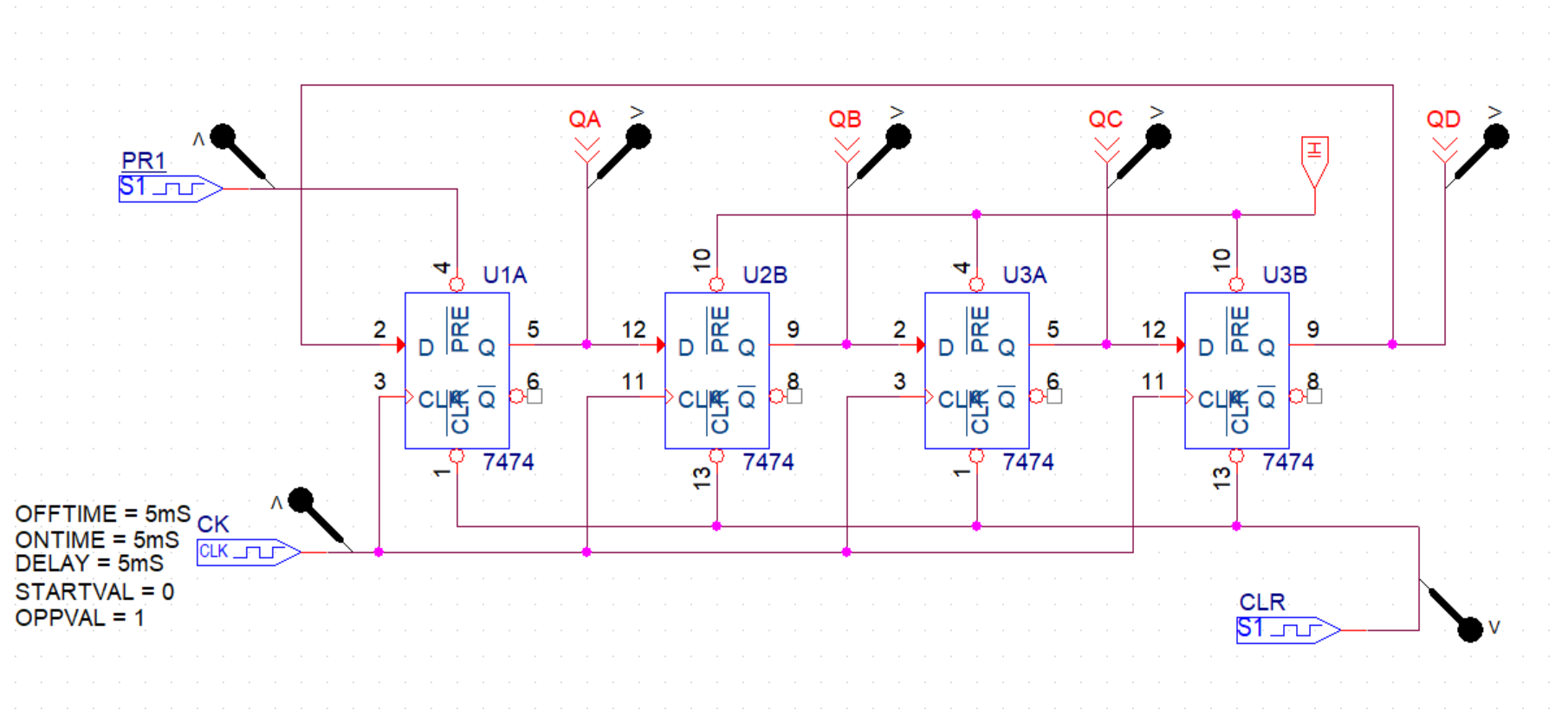

2. 링카운터

회로도와 SCHEMATIC

링카운터 시뮬레이션 설정과 결과

1) 40ms로 설정했을 때

2) 80ms로 설정했을 때

< 비동기 카운터 >

1. 4진 비동기 업 카운터

회로도와 SCHEMATIC

4진 비동기 업 카운터 시뮬레이션 설정과 결과

2. 4진 비동기 다운 카운터

회로도와 SCHEMATIC

4진 비동기 다운 카운터 시뮬레이션 설정과 결과

D 플립플롭, JK 및 T 플립플롭, 시프트 레지스터, 비동기 카운터(4진 비동기 업, 다운 카운터) 끝!