2024.10.24 수업날

< 인버터 Mask Set >

nmos와 pmos 2개가 이어져 각 MOSFET의 입력에 따라 output이 결정된다.

input은 A, output은 Y로 나타낸다.

인버터의 Mask Set은 아래와 같이 6종류의 mask가 사용된다.

위에서부터 순서대로 nwell, ploy, n+, p+, contact, metal 이다.

< layout >

- 회로도를 원하는 모양으로 만들기 위한 2차원의 그림

- Chip은 Mask의 설정으로 지정된다.

- Mask의 최소 크기는 트랜지스터 크기를 결정하는데, 그에 따라 속도, 비용 및 전력을 결정한다.

- 최소한의 면적 구조 layout을 만들수록 집적도가 높다.

- 회로도가 같더라도 layout은 달라질 수 있으며, 다양한 방법으로 면적을 줄일 수 있다.

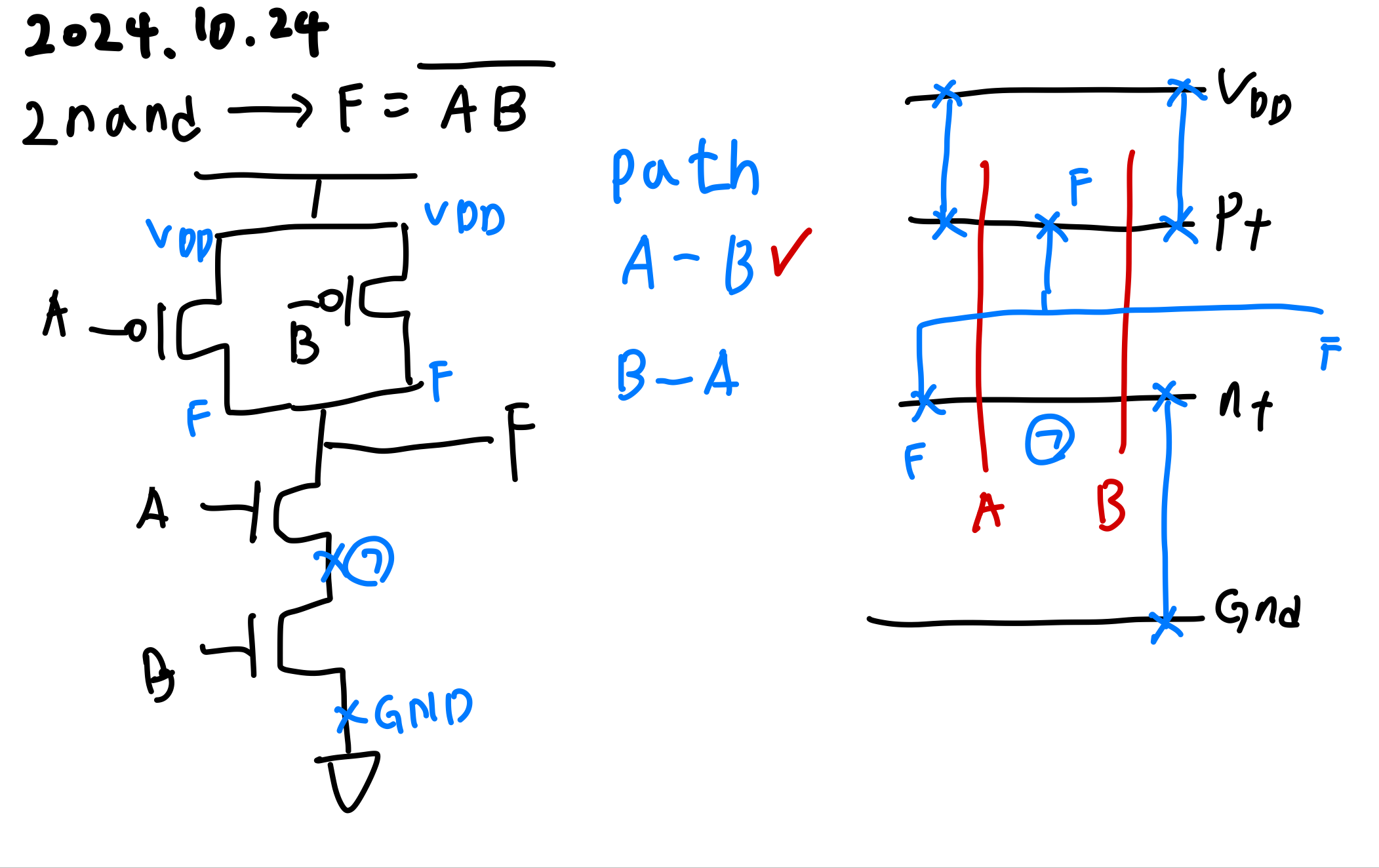

< Stick Diagrams >

- layout을 만들기 전, 계획하는 단계

- 진행 순서

1) 출력 F에 해당하는 CMOS schematic를 그린다.

2) 각 입력값(A, B, C...)이 인접한 순서를 찾아서 path를 지정한다. path가 여러개 나와도 상관없다.

3) 위에서부터 순서대로 VDD, P+, N+, GND를 나타내는 가로선을 새로 그리고, path에서 지정한 순서대로 좌측부터 입력값을 세로선으로 추가한다.

4) CMOS schematic을 보면서 입력값과 인접한 곳(VDD, GND, F...)이 어디인지를 표시한 후, Stick Diagrams에 표시한다.

5) 인접한 곳이 같다면 서로 이어준다.

< 다양한 Stick Diagrams 그려보기 >

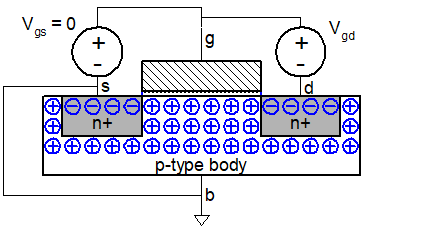

< MOS Capacitor >

- Gate와 Body는 MOS capacitor를 형성한다.

- 위에서부터 순서대로 Accumulation, Depletion, Inversion의 작동 단계이다.

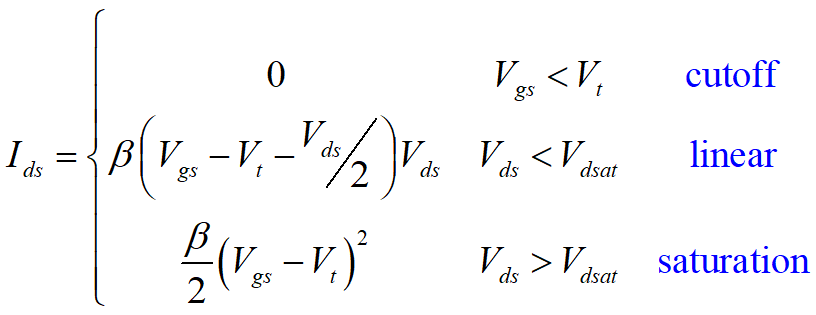

< nMOS I-V Characteristics >

1. nmos cutoff

- Channel은 없다.

- I = 0

2. nmos linear

- Vds에 따라 Ids가 증가한다.

3. nmos saturation

- 전류가 포화상태

- 전류 source와 유사하다.

4. nMOS I-V Summary

< pMOS I-V Characteristics >

- pmos의 경우 모든 doping과 전압이 반전된다.

- 일반적으로 mn 보다 2~3배 낮다.

- 따라서 동일한 전류를 제공하려면 pmos가 더 넓어야 한다.

- mn / mp = 2 라고 가정

< Capacitance >

- 물체가 전하를 축적하는 능력을 나타내는 물리량

- 절연체로 분리된 두 도체에는 정전용량이 있는데, 작동에 필요한 channel 전하를 생성한다.

- Source와 Drain에는 본체에 대한 정전 용량이 있다.

- 역바이어스 다이오드 전반에 걸쳐 Source / Drain 확산과 연관되어 있기 때문에 확산 capacitance라고 한다.

< cadence tool 사용하기 >

cadence를 실행했으면, gpdk090을 기반으로 한 Library를 추가한다.

맨 처음 생성했을때는 cell과 view가 비어있다.

Library Manager에서 File -> New에서 Cell View을 선택한다.

이번에는 NOT의 schematic을 그려본다.

단축키 I를 눌러서 nmos 1v, pmos 1v를 추가하고,

단축키 W를 눌러서 wire로 연결해준다.

단축키 L을 눌러서 Lable을 설정하고,

단축키 P를 눌러서 Pin을 설정한다.

먼저 nmos의 total width를 1u로 설정하고, pmos의 total width를 2u로 설정한다.

다음으로 만든 schematic을 기반으로 한 symbol을 만들어본다.

Create -> Cellview -> From Cellview를 눌러서 NOT schematic을 symbol로 만든다는 것을 확인한 후

아래와 같이 입력값과 출력값을 어느 곳에 위치시킬 것인지를 설정한다.

아래와 같이 symbol을 만들면 된다.

다음으로 시뮬레이션을 실행해서 결과를 확인해본다.

이름을 바꾸고, schematic으로 설정한 파일을 새롭게 생성한다.

단축키 I를 눌러 위에서 만들었던 NOT symbol을 추가한다.

다음으로 하단에 vdc, gnd를 추가한다.

그리고 단축키 Q를 눌러서 아래와 같이 vdc의 값을 설정해준다.

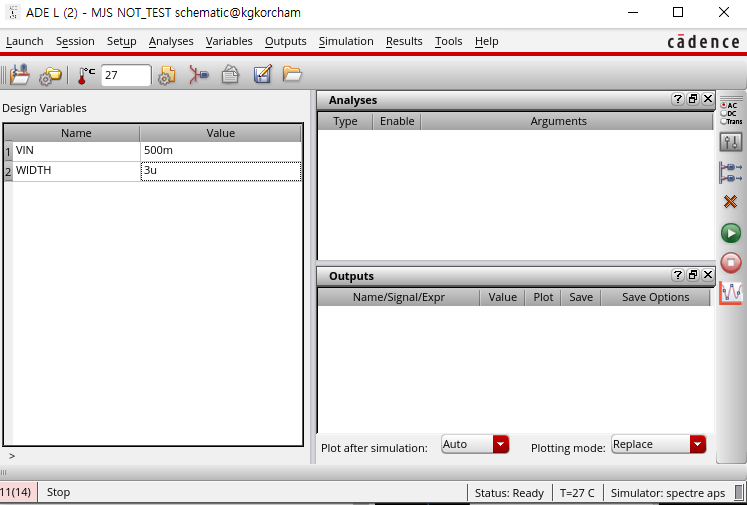

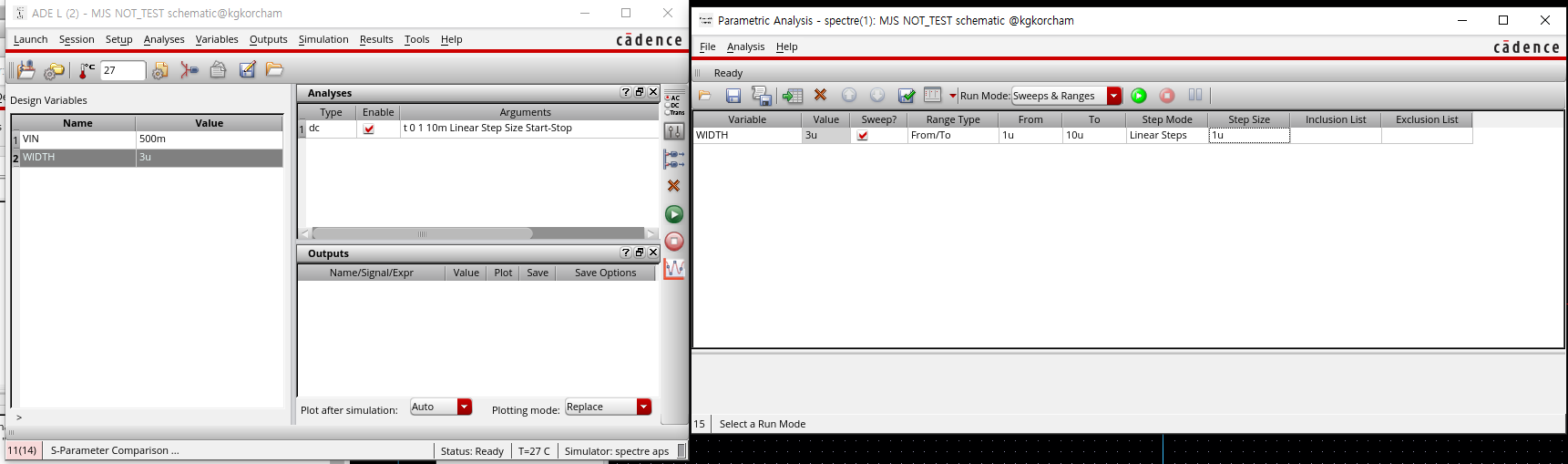

Launch -> ADE L을 선택하여 VIN에 500m를 입력하고 Analyses -> choose를 선택하여 아래와 같이 설정한다.

다음으로 ADE L 창의 우측에 있는 초록색 버튼을 누르고 Results -> Direct plot -> Main Form을 선택한다.

그리고 NOT_TEST의 schematic에서 VIN과 VOUT을 클릭하면 아래와 같이 결과가 나타난다.

NOT schematic에서 pmos의 total width를 2u로 설정했기 때문에 시뮬레이션에서 그래프가 좌측으로 치우쳐진 것을 확인할 수 있다.

이제 NOT schematic에서 pmos의 total width를 WIDTH로 설정하고 다시 시뮬레이션을 돌려보자.

NOT_TEST schematic으로 돌아와서 아래와 같이 설정해준다.

그리고 시뮬레이션을 돌릴 범위를 설정할 수 있는데, Tools -> parametric analysis를 선택해서 처음에는 1u ~ 10u에서 1u 간격으로 시뮬레이션을 실행해본다. 그리고 500m에서 가장 가까운 VOUT의 값을 소숫점 둘째자리까지 구한다.

따라서 500m에서 가장 가까운 VOUT은 2.91u인 것을 확인할 수 있다.

다시 NOT schematic으로 돌아와서 pmos의 total width를 2.91u로 설정한다.

인버터 Mask Set, layout, Stick Diagrams, MOS Capacitor, nMOS와 pMOS I-V Characteristics, Capacitance, Virtuoso 툴 사용하기 끝!